When shifting left, the most-significant bit is lost, and a 0 bit is inserted on the other end. The left shift operator is usually written as '. The fraction including the non stored bit is called a significand. The exponent is stored as a biased value, not a signed value. The 8-bit has 127 added, the 11-bit has 1023 added. A few values of the exponent are 'stolen' for special values, +/- infinity, not a number, etc. Floating point numbers are sign magnitude. Invert the sign bit to negate.

. After studying this section, you should be able to:. Understand ones complement notation. Sign bit. Value range.

Ones complement arithmetic. End around carry. Understand ones complement notation. Additive inverse. Twos complement addition. Twos complement subtraction. Negative results.

Overflow situations. Flag registers.Ones ComplementThe complement (or opposite) of +5 is −5.

When representing positive and negative numbers in 8-bit ones complement binary form, the positive numbers are the same as in signed binary notation described in i.e. The numbers 0 to +127 are represented as 00000000 2 to 01111111 2.

Single FW Image Support2. Wireless HT 20/40 Co-existence3. D link dir 600 dd wrt b5. Fix double NAT issue under IPv6 connection.Enhancements: 1. Add some more IPV6 Feature 4.

However, the complement of these numbers, that is their negative counterparts from −127 to −0, are represented by ‘complementing’ each 1 bit of the positive binary number to 0 and each 0 to 1. For example:+5 10 is 00000101 2−5 10 is 11111010 2Notice in the above example, that the most significant bit (msb) in the negative number −5 10 is 1, just as in signed binary. The remaining 7 bits of the negative number however are not the same as in signed binary notation. They are just the complement of the remaining 7 bits, and these give the value or magnitude of the number. 1.5.1 Adding Positive & Negative Numbers in Ones ComplementFig. 1.5.1 shows the result of adding −4 to +6, using ones complement,(this is the same as subtracting +4 from +6, and so it is crucial to arithmetic).The result, 00000001 2 is 1 10 instead of 2 10.This is better than subtraction in signed binary, but it is still not correct. The result should be +2 10 but the result is +1 (notice that there has also been a carry into the none existent 9th bit).Fig.

1.5.2 shows another example, this time adding two negative numbers −4 and −3.Because both numbers are negative, they are first converted to ones complement notation.+4 10 is 00000100 in, so complementing gives 11111011. 1.5.2 Adding Negative Numbers in Ones ComplementThis is −4 10 in ones complement notation.+3 10 is 00000011 in pure 8 bit binary, so complementing gives 11111100.This is −3 10 in ones complement notation.The result of 11110111 2 is in its complemented form so the 7 bits after the sign bit (1110111), should be re-complemented and read as 0001000, which gives the value 8 10. As of the result is 1 the result must be negative, which is correct, but the remaining seven bits give the value of −8. This is still wrong by 1, it should be −7.

End Around CarryThere is a way to correct this however. Whenever the ones complement system handles negative numbers, the result is 1 less than it should be, e.g. 1 instead of 2 and −8 instead of −7, but another thing that happens in negative number ones complement calculations is that a carry is ‘left over’ after the most significant bits are added. Instead of just disregarding this carry bit, it can be added to the least significant bit of the result to correct the value. This process is called ‘end around carry’ and corrects for the result -1 effect of the ones complement system.There are however, still problems with both ones complement and signed binary notation. The ones complement system still has two ways of writing 0 10 (00000000 2 = +0 10 and 11111111 2 = −0 10); additionally there is a problem with the way positive and negative numbers are written.

In any number system, the positive and negative versions of the same number should add to produce zero. As can be seen from Table 1.5.1, adding +45 and −45 in decimal produces a result of zero, but this is not the case in either signed binary or ones complement.This is not good enough, however there is a system that overcomes this difficulty and allows correct operation using both positive and negative numbers. This is the Twos Complement system. Twos Complement NotationTwos complement notation solves the problem of the relationship between positive and negative numbers, and achieves accurate results in subtractions.To perform binary subtraction, the twos complement system uses the technique of complementing the number to be subtracted. In the ones complement system this produced a result that was 1 less than the correct answer, but this could be corrected by using the ‘end around carry’ system. This still left the problem that positive and negative versions of the same number did not produce zero when added together.The twos complement system overcomes both of these problems by simply adding one to the ones complement version of the number before addition takes place.

The process of producing a negative number in Twos Complement Notation is illustrated in Table 1.5.2. 1.5.3 Adding a Number to its Twos Complement Produces ZeroThis version of −5 now, not only gives the correct answer when used in subtractions but is also the additive inverse of +5 i.e. When added to +5 produces the correct result of 0, as shown in Fig. 1.5.3Note that in twos complement the (1) carry from the most significant bit is discarded as there is no need for the ‘end around carry’ fix.With numbers electronically stored in their twos complement form, subtractions can be carried out more easily (and faster) as the microprocessor has simply to add two numbers together using nearly the same circuitry as is used for addition.6 − 2 = 4 is the same as (+6) + (−2) = 4.

1.5.5 Subtracting a Positive Number from a Larger Positive NumberFig. 1.5.5 shows the simplest case of twos complement subtraction where one positive number (the subtrahend) is subtracted from a larger positive number (the minuend).

In this case the minuend is 17 10 and the subtrahend is 10 10.Because the minuend is a positive number its sign bit (msb) is 0 and so it can be written as a pure 8 bit binary number.The subtrahend is to be subtracted from the minuend and so needs to be complemented (simple ones complement) and 1 added to the least significant bit (lsb) to complete the twos complement and turn +10 into −10.When these three lines of digits, and any carry 1 bits are added, remembering that in twos complement, any carry from the most significant bit is discarded. The answer (the difference between 17 and 10) is 00000111 2 = 7 10 which is correct. Therefore the twos complement method has provided correct subtraction by using only addition and complementing, both operations that can be simply accomplished by digital electronic circuits.

Subtraction with a negative result. 1.5.6 Subtraction Producing a Negative ResultSome subtractions will of course produce an answer with a negative value. 1.5.6 the result of subtracting 17 from 10 should −7 10 but the twos complement answer of 11111001 2 certainly doesn’t look like −7. However the sign bit is indicating correctly that the answer is negative, so in this case the 7 bits indicating the value of the negative answer need to be 'twos complemented' once more to see the answer in a recognisable form.When the 7 value bits are complemented and 1 is added to the least significant bit however, like magic, the answer of 10000111 2 appears, which confirms that the original answer was in fact −7 in 8 bit twos complement form.It seems then, that twos complement will get the right answer in every situation?Well guess what − it doesn’t! There are some cases where even twos complement will give a wrong answer. In fact there are four conditions where a wrong answer may crop up:1.When adding large positive numbers.2.When adding large negative numbers.3.When subtracting a large negative number from a large positive number.4.When subtracting a large positive number from a large negative number.The problem seems to be with the word ‘large’. What is large depends on the size of the digital word the microprocessor uses for calculation.

As shown in Table 1.5.3, if the microprocessor uses an 8−bit word, the largest positive number that can appear in the problem OR THE RESULT is +127 10 and the largest negative number will be −128 10. The range of positive values appears to be 1 less than the negative range because 0 is a positive number in twos complement and has only one occurrence (00000000 2) in the whole range of 256 10 values.With a 16-bit word length the largest positive and negative numbers will be +32767 10 and -32768 10, but there is still a limit to the largest number that can appear in a single calculation. 1.5.7 Carry Overflows into Sign BitIn this example, the two numbers to be added (115 10 and 91 10) should give a sum of 206 10 and at first glance 11001110 2 looks like the correct answer of 206 10,but remember that in the 8 bit twos complement system the most significant bit is the sign of the number, therefore the answer appears to be a negative value and reading just the lower 7 bits gives 1001110 2 or -78 10.

Although twos complement negative answers are not easy to read, this is clearly wrong as the result of adding two positive numbers must give a positive answer.According to the information in Fig 1.5.6, as the answer is negative, complementing the lower 7 bits of 11001110 2 and adding 1 should reveal the value of the correct answer, but carrying out the complement+1 on these bits and leaving the msb unchanged gives 10110010 2 which is -50 10. This is nothing like the correct answer of 206 10 so what has happened?The 8 bit twos complement notation has not worked here because adding 115 + 91 gives a total greater than +127, the largest value that can be held in 8-bit twos complement notation.What has happened is that an overflow has occurred, due to a 1 being carried from bit 6 to bit 7 (the most significant bit, which is of course the sign bit), this changes the sign of the answer. Additionally it changes the value of the answer by 128 10 because that would be the value of the msb in pure binary. So the original answer of 78 10 has ‘lost’ 128 10 to the sign bit. The addition would have been correct if the sign bit had been part of the value, however the calculation was done in twos complement notation and the sign bit is not part of the value.Of course in real electronic calculations, a single byte overflow situation does not usually cause a problem; computers and calculators can fortunately deal with larger numbers than 127 10. They achieve this because the microprocessors used are programmed to carry out the calculation in a number of steps, and although each step must still be carried out in a register having a set word length, e.g.

8 bits or 16 bits, corrective action can also be taken if an overflow situation is detected at any stage.Microprocessors deal with this problem by using a special register called a status register, flag register or conditions code register, which automatically flags up any problem such as an overflow or a change of sign, that occurs. It also provides other information useful to the programmer, so that whatever problem occurs; corrective action can be taken by software, or in many cases by firmware permanently embedded within the microprocessor to deal with a range of math problems.Whatever word length the microprocessor is designed to handle however, there must always be a limit to the word length, and so the programmer must be aware of the danger of errors similar to that described in Fig. A typical flag register is illustrated in Fig. 1.5.8 and consists of a single 8-bit storage register located within the microprocessor, in which some bits may be set by software to control the actions of the microprocessor, and some bits are set automatically by the results of arithmetic operations within the microprocessor.

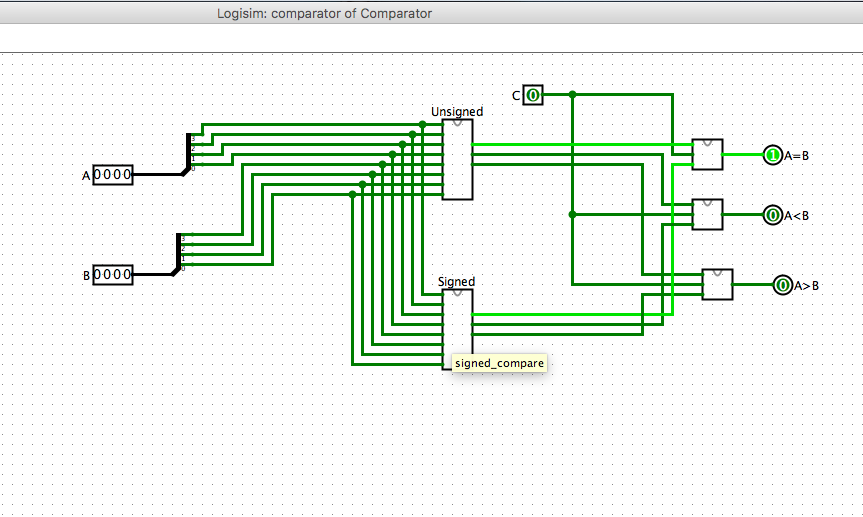

A magnitude digital Comparator is a combinational circuit that compares two digital or binary numbers in order to find out whether one binary number is equal, less than or greater than the other binary number. We logically design a circuit for which we will have two inputs one for A and other for B and have three output terminals, one for A B condition, one for A = B condition and one for A. The truth table for a 1-bit comparator is given below:From the above truth table logical expressions for each output can be expressed as follows:AB: AB'A.

From the above truth table K-map for each output can be drawn as follows:From the above K-maps logical expressions for each output can be expressed as follows:AB:A1B1’ + A0B1’B0’ + A1A0B0’A=B: A1’A0’B1’B0’ + A1’A0B1’B0 + A1A0B1B0 + A1A0’B1B0’: A1’B1’ (A0’B0’ + A0B0) + A1B1 (A0B0 + A0’B0’): (A0B0 + A0’B0’) (A1B1 + A1’B1’): (A0 Ex-Nor B0) (A1 Ex-Nor B1)AB can be possible in the following four cases:. If A3 = 1 and B3 = 0.

If A3 = B3 and A2 = 1 and B2 = 0. If A3 = B3, A2 = B2 and A1 = 1 and B1 = 0. If A3 = B3, A2 = B2, A1 = B1 and A0 = 1 and B0 = 0Similarly the condition for A.